1.5 ALU 算术逻辑单元 (How Computers Calculate)

ALU 算术逻辑单元(Arithmetic and Logic Unit)是计算机中负责运算的组件。

最著名的 ALU 之一是 Intel 74181,其于 1970 年发布,是第一个封装在单个芯片中的完整 ALU。 Intel 74181 使用了 70 个逻辑门,但无法执行乘除运算。

ALU 由 1 个算术单元(arithmetic)和 1 个逻辑单元(logic unit)组成,算术单元可用于进行加减法运算或是增量运算(x+1),逻辑单元执行逻辑操作(如布尔代数中的基本运算)。

1.5.1 算术单元

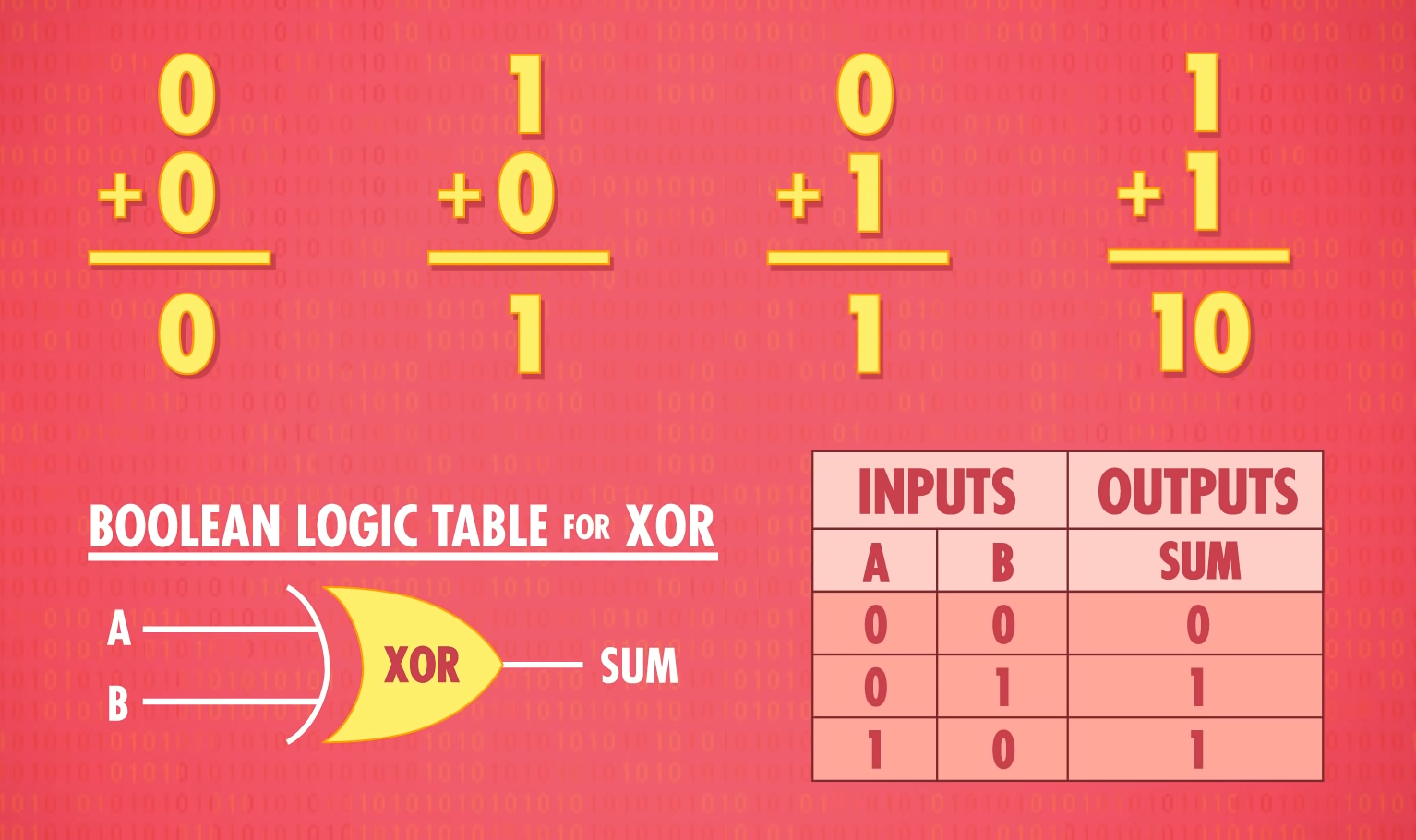

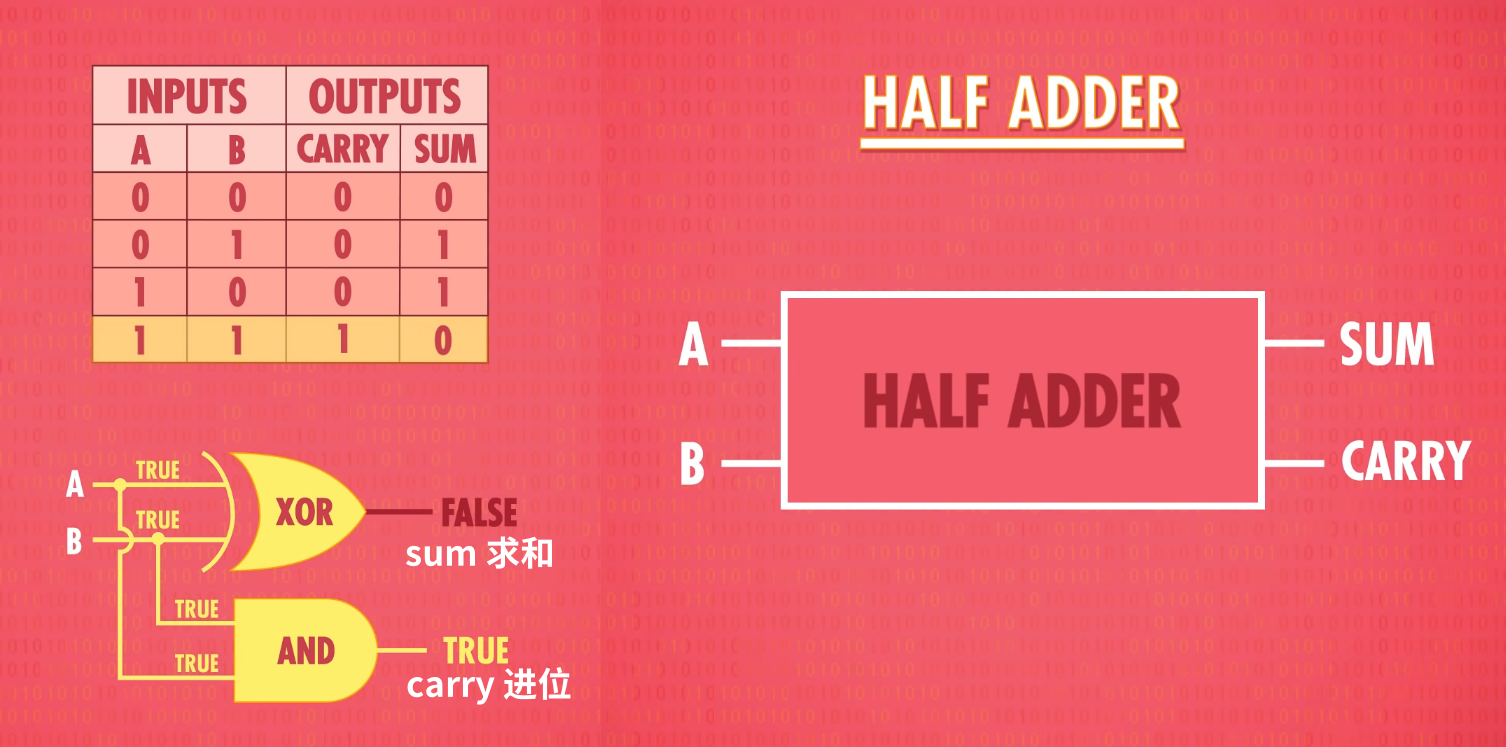

半加器

半加器(half adder)由异或门和与门组成,仅能计算 1 位加法。两个输入(0 或 1)有 4 种可能的输出(1 = true,0 = false),不计进位的情况(1+1=0,高位舍弃)可用「异或门」搭建:

当且仅当两个输入均为 1 时需要进位,该规则和「与门」相同,两者连接则为半加器:

全加器

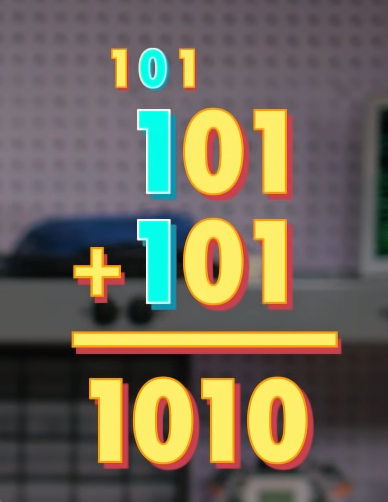

使用半加器做两个三位二进制数加法时,需要多加一个进位上的数字(共计 3 个数相加)。

全加器的真值表如下:

全加器的逻辑门电路如下:

8 位行波进位加法器

全加器可以处理两个三位二进制数的加法运算,两个八位二进制数的加法可以从低位逐列相加,用 1 个半加器和 7 个全加器搭建:

当计算结果的位数大于可用于表示的位数,则会出现「溢出」(overflow),这会导致 error 和不可预期的结果。

为防止溢出,可以使用更多的全加器来完成 16 位或是 32 位数字的操作。但使用更多的逻辑门会提高造价,同时进位计算的耗时也更多,在每秒几十亿次的运算下该延迟仍然会造成影响。所以现代计算机所采用的加法电路为「超前进位加法器」(carry-look-ahead),其速度更快。

乘除法

ALU 的算术单元基本都支持下图中的 8 种操作,简单 ALU 可以通过累加/累减来实现四则运算中的乘除法(慢但有效),复杂 ALU 会用更多的逻辑门构建乘法电路。

1.5.2 逻辑单元

逻辑单元(logic unit)用于执行逻辑操作,比 AND、OR 和 NOT 操作,也可以用于进行简单的数值测试。注意此处的 0 和 1 遵守布尔代数的逻辑运作,而非算术加减。

下图的逻辑单元门电路用于检测输出是否为 0(可用于确认两数字是否相等),OR 或门遇 1 出 1,最后用 NOT 非门取反后,凡有 1 则为 0,检测结果为 False 假,意为输出不为 0(其中至少有一位是 1)。

1.5.3 ALU 抽象

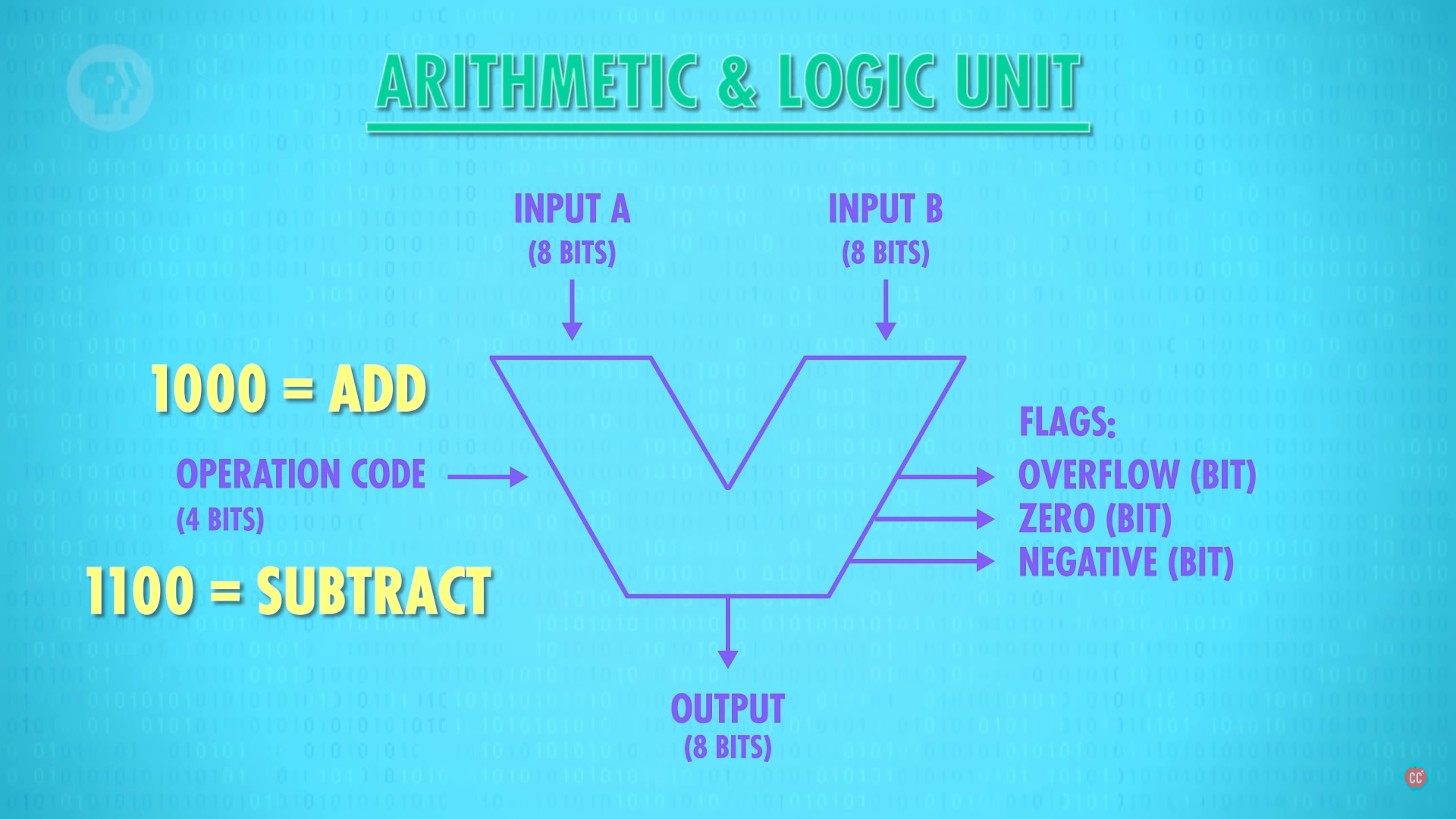

8 位 ALU 需要用上百个逻辑门搭建,因此工程师用镂空大 V 符号来表示 ALU 组件:

简图如下:

除了两个 8 位的输出和一个输入之外,8 位 ALU 还需要用 4-bits「操作码」(Operation Code)确认执行操作类型,同时还会输出一些 1-bit 的标志位(Flags)表示特定状态,常见类型如下:

- 溢出位(Overflow)检测是否发生溢出情况。

- 零标志位(Zero):检测输出是否为零。

- 负标志位(Negative):检测输出是否为负数。